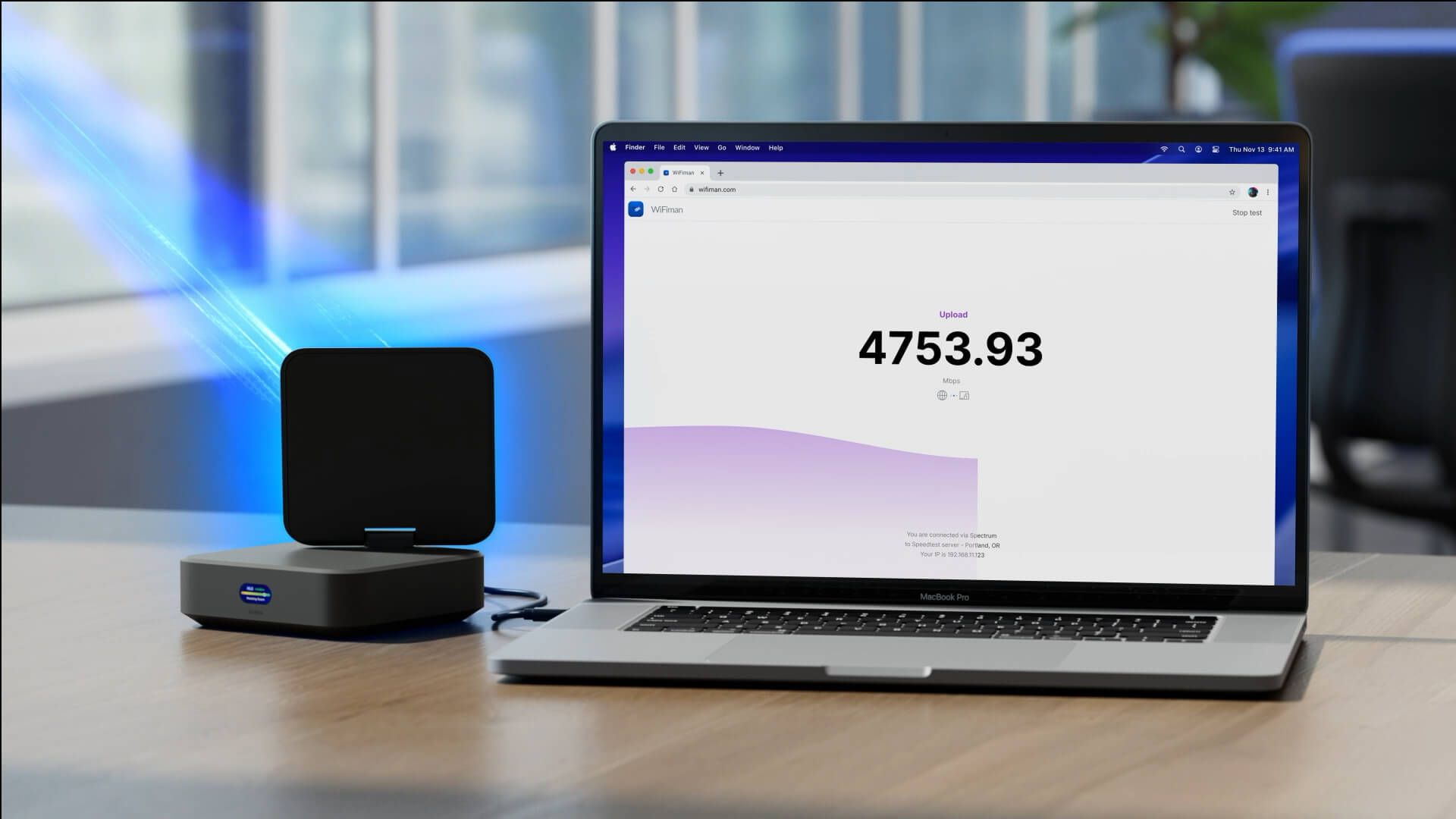

Ubiquiti AirWire: WiFi-7-Boost mit neuem Gerät

Ubiquiti will die WiFi 7-Infrastruktur zu ihrem vollen Potenzial verhelfen. Das neue AP soll Client-Geräten mit Multi-Link Operation (MLO) unterstützen und mehr als nur eine Verbindung nutzen. Diese Einschränkung begrenzt den Durchsatz und verhindert eine wirklich hochzuverlässige, aggregierte Multi-Gigabit-Wireless-Leistung.