Intel Xeon Clearwater Forest (Bild © Chipsandcheese, Intel)

Intel Xeon Clearwater Forest (Bild © Chipsandcheese, Intel)

Architektur auf einen Blick

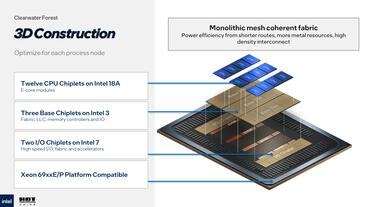

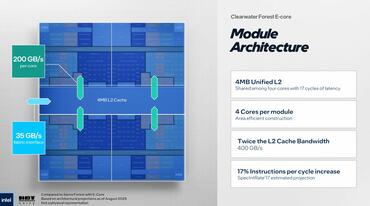

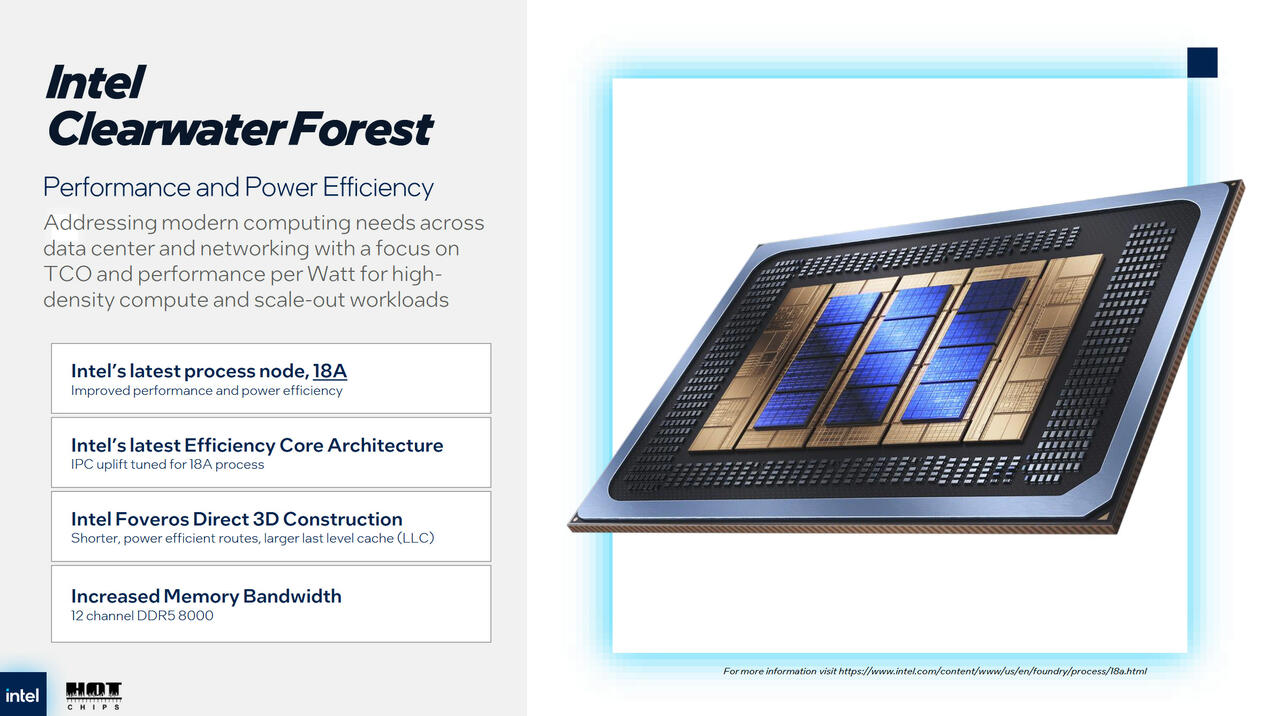

Clearwater Forest wird die “Crestmont” E-Cores der Sierra Forest-Serie durch “Skymont” ersetzen und bietet eine breitere Pipeline und eine größere Reorder-Kapazität, die die Single-Thread-Lücke zu P-Cores verringert und gleichzeitig die Vorteile der Small-Core-Dichte beibehält. Skymont ist in Quad-Core-Clustern mit einem gemeinsamen 4 MB L2 angeordnet. Sechs Cluster bilden einen Rechen-Die mit 24 Kernen und Intel integriert gleich vier solcher Rechen-Dies pro Basis-Die. Mit drei Basis-Dies pro Package erreicht die volle Konfiguration stolze 288 E-Kerne, was doppelt so viele ist, wie noch bei “Sierra Forest” mit seinen 144 Kernen.

3D-Stacking und Cache-Topologie

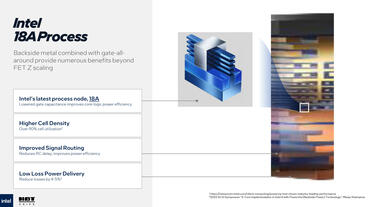

Die Rechen-Dies werden in Intel 18A-Verfahren hergestellt und sind über drei Intel-Basis-Dies gestapelt, die die Mesh-Struktur und die L3-Cache-Slices tragen. Durch das Verschieben des L3-Caches in die Basisschicht wird Recheneinheit-Fläche frei und es stehen 8 MB L3 pro Slice zur Verfügung, was insgesamt in 576 MB L3-Kapazität pro Package resultiert. Die Verbindungen zwischen den Schichten verwenden einen dichten etwa 9 μm Bonding-Pitch. Die Basis-Dies sind vertikal über eingebettete Siliziumbrücken mit einem 45 μm Pitch miteinander verbunden, wodurch sich das Mesh über den gesamten Stack erstreckt.

Die Speichercontroller befinden sich an den Rändern des Basis-Dies und L3-Slices sind auf nahegelegene Controller ausgerichtet. Dieses Design reduziert sowohl die durchschnittliche Speicherlatenz als auch die NUMA-Partitionierung.

Interconnect-, Bandbreiten- und Latenzdynamik

Innerhalb eines Clusters entspricht die L2-Bandbreite pro Kern der von Crestmont, aber die aggregierte Bandbreite steigt. Clearwater Forest steigert außerdem die Parallelität mit bis zu 128 L2-Misses pro Cluster, um die Fabric- und DRAM-Latenz besser zu verbergen. Intel gibt eine Fabric-Bandbreite von etwa 35 GB/s pro Cluster an und interne Labortests ergaben etwa 1,3 TB/s für DRAM-Lesevorgänge mit DDR5-8000, was eine gute Zahl für eine Serverkonfiguration darstellt, bei der die Dichte im Vordergrund steht. Beim L3-Cache ist die Kapazität gegeben, aber die Latenz dürfte größer sein als bei Desktop-Designs, sodass der vergrößerte 4-MB-L2-Speicher für die Trefferquote und die Steuerung der Tail-Latenz entscheidend ist.

In Dual-Socket-Systemen bieten UPI-Verbindungen bis zu 576 GB/s Cross-Socket-Bandbreite, was eine erhebliche Steigerung gegenüber den typischen NUMA-Werten früherer Plattformen darstellt.

IO und Wiederverwendung der Plattform

Clearwater Forest bietet 96 PCIe 5.0-Lanes pro Sockel, wobei 64 Lanes CXL für Memory Pooling oder den Anschluss von Beschleunigern bieten. Die aggregierte Plattform-IO kann ca. 1 TB/s erreichen. Die IO-Dies basieren auf Intel 7 Fertigung und werden aus Sierra Forest wiederverwendet, was die Strategie von AMD widerspiegelt, die IO-Entwicklung über Generationen hinweg zu optimieren.

Produktpositionierung

Skymont-Kerne setzen beim Silizium auf Intel 18A-Fertigung für Server und TSMC N3 in Client-Segment (Arrow Lake), was einen prozessunabhängigen Kernansatz signalisiert, der die Mikroarchitektur von einem einzelnen Fab-Knoten entkoppelt. Für Clearwater Forest bedeutet dies, dass mehr Kerne auf weniger Fläche untergebracht werden können, wobei die Vorteile der Stromversorgung, für die 18A ausgelegt ist, zum Tragen kommen.

Mit den neuen für Clearwater Forest-Kernen wird Intel einen weiteren Boost seiner Leisung erreichen, aber auch bei IO und Kern-Dichte nachlegen. Der hohe Cache sollte auch nicht untershcätzt werden, auch wen AMD hier wohl noch mehr liefern wird als Intel. Das Upgrade-Potenzial sollte groß genug sein, jedoch müsste man abwarten, wie die Realwerte aus dem Markt am Ende aussehen werden.