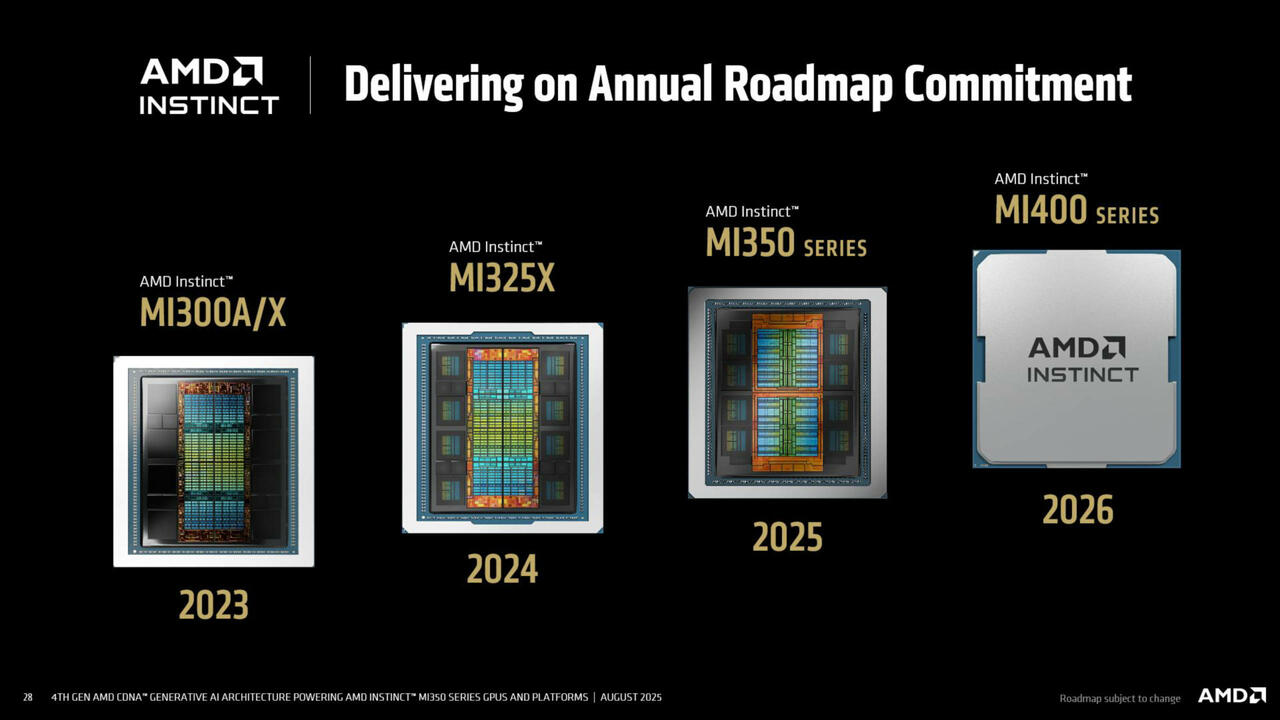

AMD Instinct MI350 MI400 Roadmap (Bild © AMD)

AMD Instinct MI350 MI400 Roadmap (Bild © AMD)

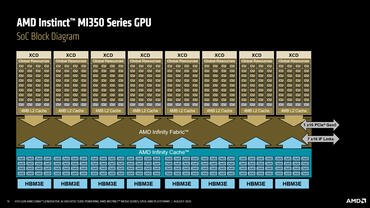

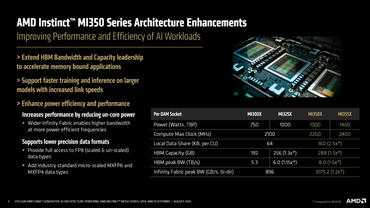

Die Produktpalette gliedert sich in den luftgekühlten MI350X (bis zu 2,2 GHz, 1000 W TBP) und den direkt flüssigkeitsgekühlten MI355X (bis zu 2,4 GHz, 1400 W TBP). Beide haben ein 3D-Multi-Chiplet-Layout auf COWOS-S: acht Accelerator Complex Dies (XCDs), die auf TSMC N3P basieren, liegen neben zwei I/O-Basis-Dies auf TSMC N6, was eine Gesamtzahl von fast 185 Milliarden Transistoren ergibt.

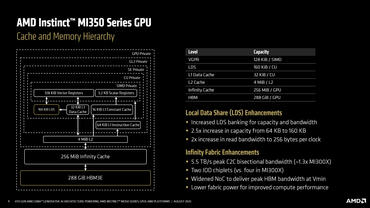

Jeder Beschleuniger hat acht HBM3e-Stacks (12-Hi, jeweils 36 GB), was insgesamt 288 GB On-Package-Speicher und bis zu 8,0 TB/s Bandbreite ergibt. Die I/O-Dies sind über Infinity Fabric AP mit 5,5 TB/s Bisektionsbandbreite verbunden und haben 256 MB Infinity Cache. Die Host-Konnektivität wird durch PCIe Gen5 x16 (128 GB/s) gewährleistet.

Für KI-Skalierung optimierte Rechenblöcke und Datenformate

CDNA 4 organisiert die GPU als 8 XCDs × 32 Recheneinheiten (insgesamt 256 CUs) und 1.024 Matrixkerne. Die Präzisionsunterstützung umfasst die Formate FP16/BF16, FP8, INT8/INT4 und die von AMD entwickelten mikroskalierten MXFP6/MXFP4-Formate, die darauf ausgelegt sind, den Durchsatz zu steigern und gleichzeitig die Genauigkeitsbudgets moderner LLMs zu verwalten.

Die interne Speicherhierarchie umfasst insgesamt 131 MB Vektorregister, 40 MB LDS, 8 MB L1, 32 MB L2 sowie den 256 MB Infinity Cache auf den I/O-Dies – eine Anordnung, die darauf abzielt, Matrizen zu versorgen, ohne den externen Speicher zu überlasten.

Die von AMD veröffentlichten Spitzenwerte für MI355X umfassen 2,5 PFLOPs Matrix FP16/BF16, 5,0 PFLOPs bei FP8 und 10 PFLOPs mit MXFP6/MXFP4 sowie 157,3 TFLOPs Vektor FP32/FP16 und 78,6 TFLOPs Vektor FP64.

Fabric, Skalierung und Partitionierung

Rack-Level-Designs basieren auf OAM 2.0-Modulen auf UBB-Backplanes, die bis zu acht Beschleuniger aufnehmen können. Inter-Accelerator-Verbindungen liefern 154 GB/s bidirektional pro Hop – etwa 20 % schneller als die vorherige Generation. Die Referenzplattformen von AMD mit acht Wegen bieten insgesamt 2,25 TB HBM3e und 1075 GB/s verfügbare Infinity Fabric-Bandbreite, mit Optionen für 10U-Luftkühlung (MI350X) oder 5U-Direktflüssigkeitskühlung (MI355X).

Mit der Ressourcenpartitionierung können Betreiber Speicher und Rechenleistung auf Socket-/XCD-Ebene aufteilen. Konfigurationen können mehrere isolierte „logische GPUs” zuweisen, um mehrere große Modelle gleichzeitig auszuführen, AMD hebt die Unterstützung für acht Modelle der 70B-Klasse auf einem einzelnen Knoten unter bestimmten NUMA- und Partitionierungseinstellungen hervor.

Package und Plattform-Rollout

AMD hat den Montageablauf beschrieben, von der Konstruktion des 3D-gestapelten SoC über die OAM-Integration bis hin zur endgültigen Befestigung des Kühlkörpers, bevor diese Module in UBB 2.0-Boards und Standard-EIA-Racks eingesetzt werden. Das Unternehmen positioniert MI350 als Weiterentwicklung von MI300 in Bezug auf Durchsatz und Effizienz. Öffentliche Vergleiche zeigen die behaupteten Vorteile gegenüber konkurrierenden GB200/B200-Plattformen in Bezug auf Speicherkapazität und ausgewählte Präzisionen.

Instinct MI350-Systeme sollen über Partner im dritten Quartal 2025 ausgeliefert werden. Die Nachfolgegeneration MI400 ist für 2026 geplant.