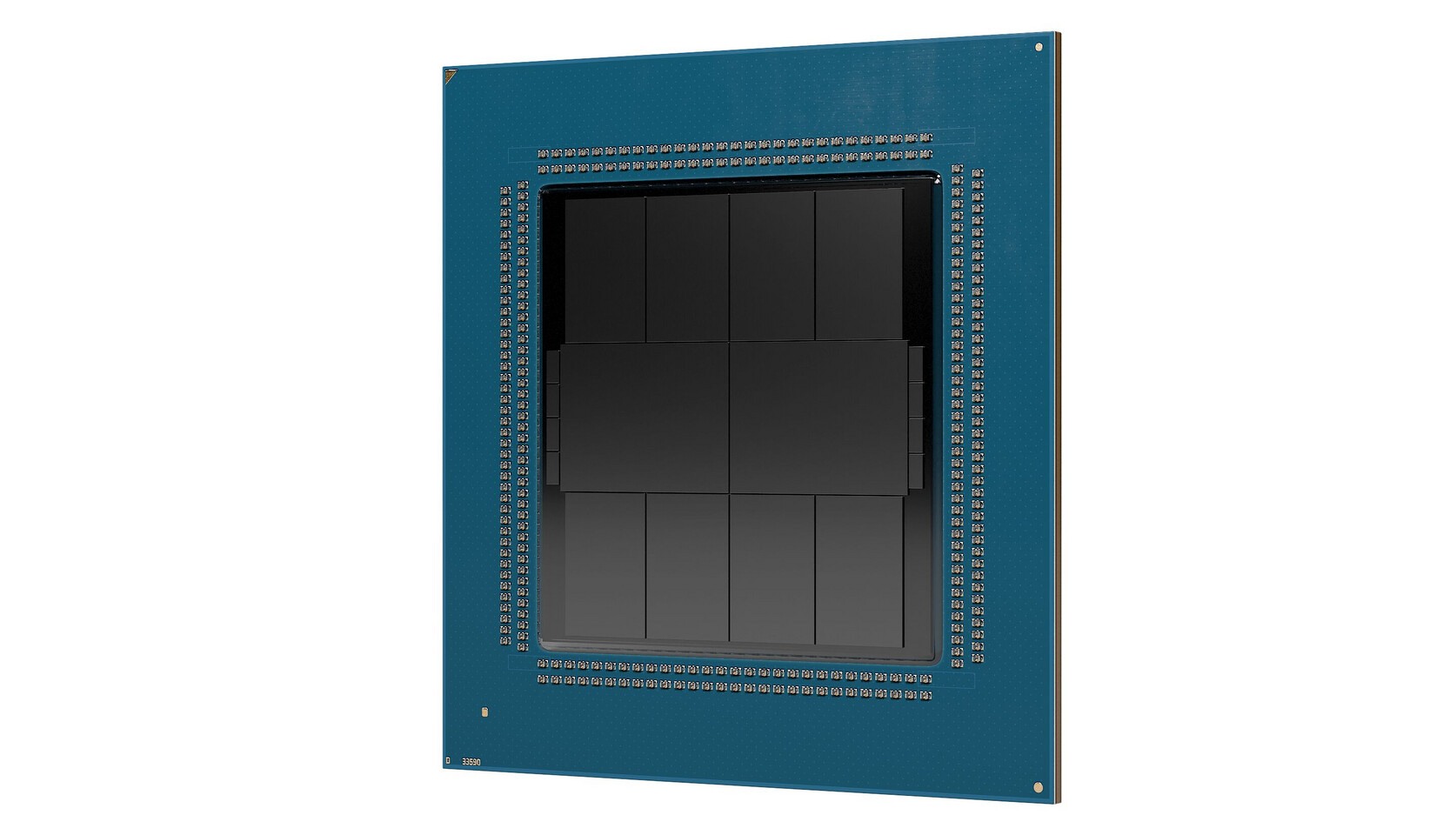

AMD EPYC Venice Zen6 CPU (Bild © AMD)

AMD EPYC Venice Zen6 CPU (Bild © AMD)

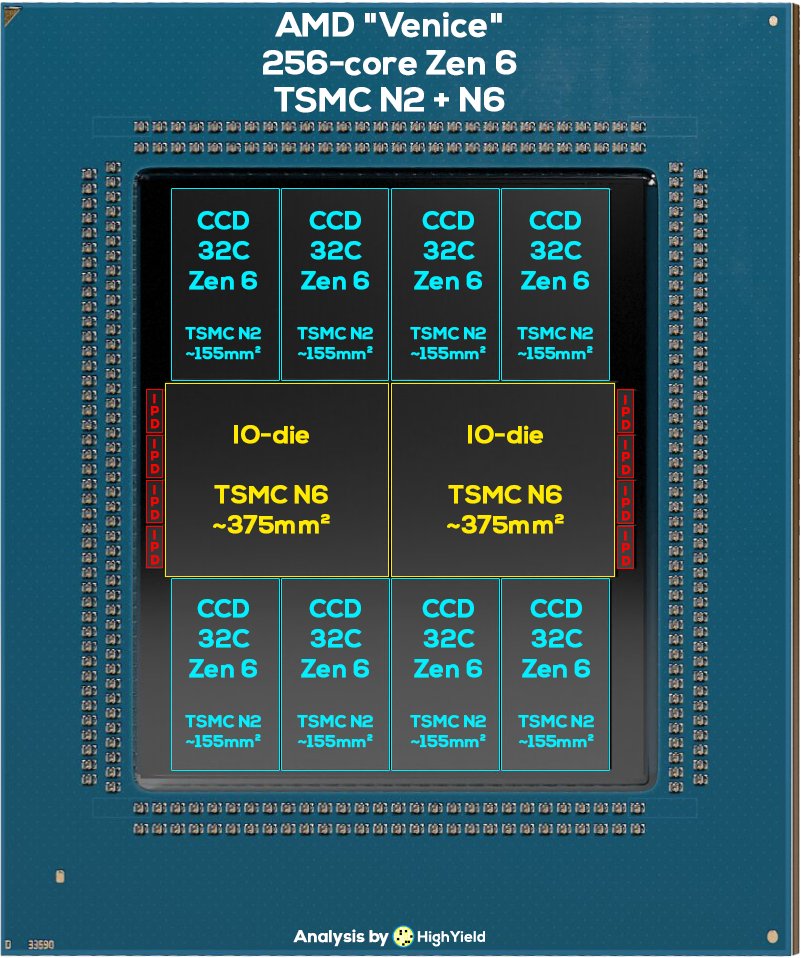

Architektur auf einen Blick

Venice bietet zwei Rechenvarianten:

- Zen 6C (Dense): Jeder CCD hat 32 Zen 6C-Kerne und 128 MB L3, was einer direkten Verdopplung der Kerne gegenüber den 16-Kern-Zen-5C-CCDs von Turin entspricht. Mit 8 CCDs erreicht das Flaggschiff 256C/512T und insgesamt 1.024 MB L3.

- Standard Zen 6: Eine zweite Variante, die auf eine höhere Leistung pro Kern abzielt, skaliert auf 192C/384T mit 16 CCDs mit jeweils 12 Kernen / 48 MB L3, was insgesamt 768 MB L3 ergibt.

Auch die Plattform-E/A wird erweitert. Venice tauscht den einzelnen ~426 mm² N6 I/O-Die von Turin gegen zwei ~375 mm² I/O-Dies (beide auf TSMC N6) aus und bietet damit erweiterte Speichercontroller, PCIe und Plattform-IP sowie AI-fokussierte Beschleuniger. Insgesamt widmet Venice etwa 750 mm² Silizium allein der I/O – ein Indikator für die Bandbreite und die Ambitionen dieser Generation im Bereich der Geräteanbindung.

Prozess- und Chipgrößen

Der Wechsel zu TSMC N2P unterstützt die Rechen-Chiplets. Ein Zen 6C CCD misst etwa 155 mm², gegenüber ~85 mm² beim Zen 5C auf N3E – eine Steigerung von ~82 %, die die doppelte Kernanzahl und den erweiterten Cache finanziert und gleichzeitig von der Energie- und Frequenzreserve eines dichteren Knotens profitiert. Der I/O-Komplex bleibt auf N6, ist jetzt aber auf zwei Chips verteilt, um Controller und Beschleuniger zu verteilen und die Stromversorgung und das Routing auf der neuen Skala von Venice zu vereinfachen.

Leistungsziele und Dichte

AMD gab für Venice eine >70 %ige Verbesserung der kombinierten Leistung/Effizienz sowie eine >30 %ige Steigerung der Thread-Dichte gegenüber der vorherigen EPYC-Generation an. Das dichte Zen 6C-Layout, der größere gemeinsame L3-Cache pro CCD und die I/O-Bandbreite auf Plattformebene sind die Hebel hinter diesen Prognosen, insbesondere für hochparallele Cloud- und HPC-Workloads.

EPYC Venice Lineup

- EPYC 9006 Venice Zen 6C: 256C/512T, bis zu 8 CCDs, 1.024 MB L3

- EPYC 9006 Venice Zen 6: 96C/192T bis 192C/384T, bis zu 16 CCDs, 384–768 MB L3

- Vorheriges Modell EPYC 9005 Turin Zen 5C: bis zu 192C/384T, 12 CCDs, 384 MB L3

- Vorheriges Modell EPYC 9005 Turin Zen 5: bis zu 96C/192T, 16 CCDs, 384 MB L3

Diese Umstrukturierung konzentriert die Rechenleistung auf weniger, aber größere CCDs für die dichte Ebene, während der Gesamtcache erweitert und ein High-Core-Mainstream-Track für gemischte Workloads beibehalten wird.

Die 256-Kern-Obergrenze und die Dual-IOD-Topologie von Venice zielen direkt auf Intels kommende Diamond Rapids (Intel 18A) Rechenzentrumsreihe ab, die voraussichtlich 192- und 256-Kern-SKUs umfassen wird. Mit 2-nm-Rechenkacheln, größerem L3 pro CCD und einem erweiterten I/O-Komplex mit On-Die-KI-Beschleunigung positioniert AMD Venice für die Konsolidierung im Front-of-Rack-Bereich, KI-nahe Dienste sowie speicher- und I/O-intensive Cloud-Bereitstellungen.