Details zur PCIe 8 0 Spezifikation (Bild © PCI-SIG)

Details zur PCIe 8 0 Spezifikation (Bild © PCI-SIG)

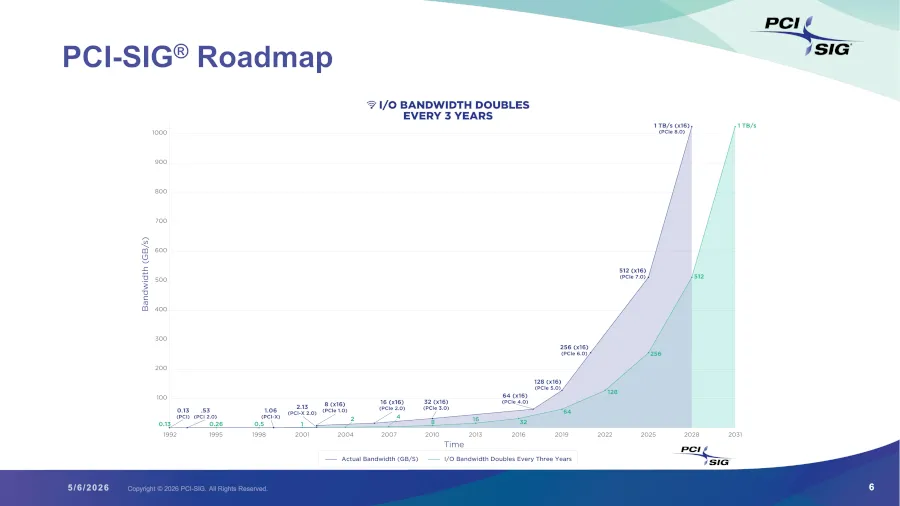

Bandbreite und Leistung

Die wichtigste Neuerung bei PCIe 8.0 ist der Sprung bei den Übertragungsgeschwindigkeiten. Der Standard zielt darauf ab, eine bidirektionale Gesamtbandbreite von 1,0 TB/s zu liefern. Dies entspricht einer Verdopplung der Kapazität von PCIe 7.0, das 512 GB/s bietet. Diese Steigerung ist entscheidend, um den wachsenden Anforderungen von Hochleistungsrechnern, KI-Beschleunigern und Rechenzentrumsarchitekturen der nächsten Generation gerecht zu werden.

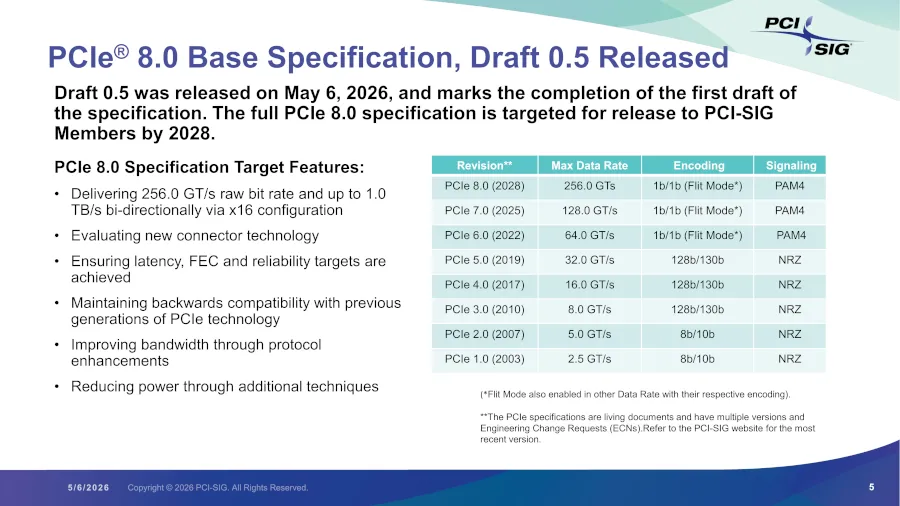

Technische Architektur und Signalübertragung

Um diese Geschwindigkeiten zu erreichen, setzt der Standard weiterhin auf fortschrittliche Signalübertragungstechniken. Wie seine Vorgänger nutzt PCIe 8.0 PAM (Pulse Amplitude Modulation), um mehr Daten in jeden Taktzyklus zu packen, ohne dass eine proportionale Erhöhung der Frequenz erforderlich ist. Das hilft dabei, die Signalintegrität und den Stromverbrauch zu kontrollieren.

| Revision | Max Data Rate | Encoding | Signalling |

|---|---|---|---|

| PCIe 8.0 (2028) | 256.0 GT/s | 1b/1b (Flit Mode*) | PAM4 |

| PCIe 7.0 (2025) | 128.0 GT/s | 1b/1b (Flit Mode*) | PAM4 |

| PCIe 6.0 (2022) | 64.0 GT/s | 1b/1b (Flit Mode*) | PAM4 |

| PCIe 5.0 (2019) | 32.0 GT/s | 128b/130b | NRZ |

| PCIe 4.0 (2017) | 16.0 GT/s | 128b/130b | NRZ |

| PCIe 3.0 (2010) | 8.0 GT/s | 128b/130b | NRZ |

| PCIe 2.0 (2007) | 5.0 GT/s | 8b/10b | NRZ |

| PCIe 1.0 (2003) | 2.5 GT/s | 8b/10b | NRZ |

Energieeffizienz und Kompatibilität

Ein zentraler Schwerpunkt der PCIe 8.0-Entwicklung ist die Reduzierung des Stromverbrauchs. Die Spezifikation untersucht neue Methoden, um den Energiebedarf pro übertragenem Datenbit zu senken, und geht damit auf die thermischen und energetischen Herausforderungen ein, die mit ultraschnellen Verbindungen verbunden sind. Darüber hinaus bleibt der Standard der Abwärtskompatibilität verpflichtet und stellt sicher, dass neue Hardware mit älteren PCIe-Steckplätzen und -Geräten weiterhin funktioniert.

Physikalische Schicht und Steckverbinder

Während die Signalübertragung weiterhin Priorität hat, evaluiert die PCI-SIG auch die physikalische Schicht. Dazu gehört die Untersuchung neuer Steckverbinder-Designs und Materialien, um Signaldämpfung und Übersprechen bei den höheren Frequenzen zu minimieren, die für einen Durchsatz von 1,0 TB/s erforderlich sind.

Aktueller Stand

Die Details wurden im Rahmen des frühen Entwurfsverfahrens (v0.5) veröffentlicht, was darauf hindeutet, dass sich die Branche in der Vorphase der Festlegung der endgültigen elektrischen und logischen Spezifikationen befindet, bevor es zur vollständigen Hardware-Implementierung und Zertifizierung übergeht.