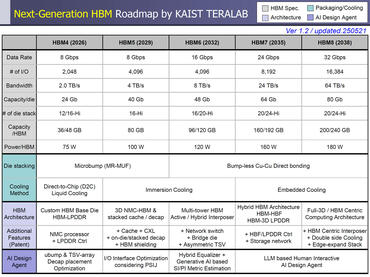

HBM Speicher Roadmap bis 2038 (Bild © KAIST & Tera)

HBM Speicher Roadmap bis 2038 (Bild © KAIST & Tera)

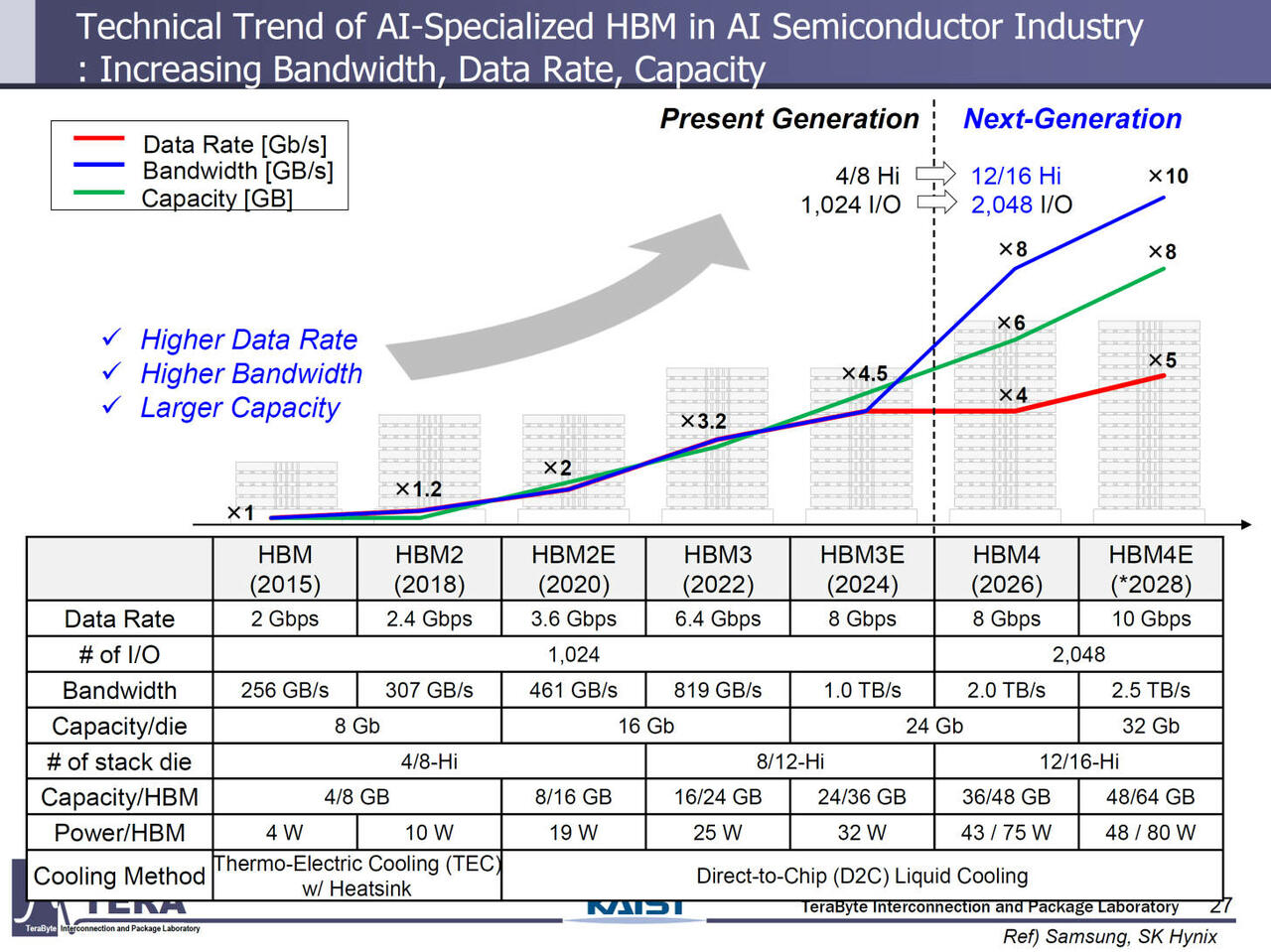

HBM4 Release in 2026

HBM4 wurde für KI-GPUs der nächsten Generation und Beschleuniger der Serverklasse entwickelt und wird über eine 2.048-Bit-Schnittstelle mit 8 Gbit/s eine Bandbreite von bis zu 2 TB/s pro Stack liefern. Mit einer Stack-Kapazität von bis zu 48 GB und einer thermischen Leistungsaufnahme von 75 W wird die frühzeitige Implementierung in den Plattformen Rubin Ultra von NVIDIA und Instinct MI500 von AMD erwartet, wobei erstere die Speicher-Stacks auf 16 verdoppeln und letztere auf insgesamt 432 GB Speicher skalieren.

Die wichtigsten Merkmale des HBM4-Speicherstandards sind:

- Datenrate: ~ 8 Gbps

- Anzahl der I/Os: 2048 (4096)

- Gesamtbandbreite: 2,0 TB/s

- Anzahl der Die-Stacks: 12/16-Hi

- Kapazität pro Die: 24 Gb

- Kapazität pro HBM: 36/48 GB

- Gehäuse-Leistung pro HBM: 75 W

- Gehäusetyp: Microbump (MR-MUF)

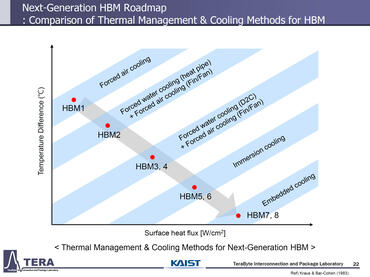

- Kühlungsmethode: Direct-To-Chip (D2C) Flüssigkeitskühlung

- Kundenspezifische HBM-Basis-Die-Architektur

- NMC-Prozessor + LPDDR im Basis-Die

- NVIDIA Rubin & Instinct MI400-Plattformen

HBM5 Release in 2029

HBM5 wird die gleiche Signalübertragungsrate von 8 Gbps beibehalten, aber die Schnittstelle auf 4.096 Bit erweitern und damit den Durchsatz pro Stack auf 4 TB/s verdoppeln. Die Stapelkapazitäten werden auf 80 GB steigen, wobei der Stromverbrauch auf 100 Watt ansteigen wird. Der kommende Feynman-Beschleuniger von NVIDIA wird voraussichtlich diese Generation implemtiert und bis zu 500 GB HBM5-Speicher integrieren. Damit wird eine Gesamtleistungsaufnahme von über 4.400 W in einem Multi-Die-Gehäuse erreichen.

Die wichtigsten Merkmale des HBM5-Speicherstandards sind:

- Datenrate: 8 Gbps

- Anzahl der I/Os: 4096

- Gesamtbandbreite: 4,0 TB/s

- Anzahl der Die-Stacks: 16-Hi

- Kapazität pro Die: 40 Gb

- Kapazität pro HBM: 80 GB

- Gehäuseleistung pro HBM: 100 W

- Verpackungsmethode: Microbump (MR-MUF)

- Kühlungsmethode: Immersionskühlung, Thermal Via (TTV), thermische Verbindung

- Spezieller Entkopplungskondensator-Chip-Die-Stack

- Kundenspezifischer HBM-Basis-Die mit 3D-NMC-HBM und gestapeltem Cache

- LPDDR+CXL im Basis-Die

- NVIDIA Feynman- und Instinct MI500-Plattformen

HBM6 Release in 2032

Mit dem für 2032 geplanten HBM6 werden die Geschwindigkeiten bei weiterhin 4.096 Bit Schnittstelle auf 16 Gbit/s steigen und 8 TB/s pro Stack liefern. Die Stapeldichte wird mit bis zu 20 Die-Lagen auf 120 GB skalieren, bei einem Stromverbrauch von 120 W. Kühlsysteme werden in dieser Phase standardmäßig Immersionslösungen und stoßfreie Kupfer-zu-Kupfer-Verbindungen verwenden.

Die wichtigsten Merkmale des HBM6-Speicherstandards sind:

- Datenrate: 16 Gbps

- Anzahl der I/Os: 4096

- Gesamtbandbreite: 8,0 TB/s

- Anzahl der Die-Stacks: 16/20-Hi

- Kapazität pro Die: 48 Gb

- Kapazität pro HBM: 96/120 GB

- Gehäuseleistung pro HBM: 120 W

- Verpackungsmethode: Bump-less Cu-Cu-Direktverbindung

- Kühlungsmethode: Immersionskühlung

- Kundenspezifische Multi-Tower-HBMs

- Aktiver/hybrider (Silizium+Glas) Interposer

- Netzwerk-Switch + Bridge-Die

HBM7 erscheint 2035

HBM7 wird mit 24 Gbps Pin-Geschwindigkeiten und einer verdoppelten 8.192-Bit-Schnittstelle einen noch aggressiveren Sprung markieren. Die Bandbreite wird auf 24 TB/s pro Stack ansteigen, wobei die Kapazität einzelner Stacks bis zu 192 GB erreichen wird. Die Leistung pro Stack steigt auf 160 W, und NVIDIA bereitet Berichten zufolge eine Plattform vor, die über 15.000 W aufnehmen kann, um diese Speicherdichten zu unterstützen.

Die wichtigsten Merkmale des HBM7-Speicherstandards sind:

- Datenrate: 24 Gbps

- Anzahl der I/Os: 8192

- Gesamtbandbreite: 24,0 TB/s

- Anzahl der Die-Stacks: 20/24-Hi

- Kapazität pro Die: 64 Gb

- Kapazität pro HBM: 160/192 GB

- Gehäuseleistung pro HBM: 160 W

- Verpackungsmethode: Bump-Less Cu-Cu-Direktverbindung

- Kühlungsmethode: Integrierte Kühlung

- Hybride HBM-Architektur

- HBM-HBF

- HBM-LPDDR

- Puffer-Dies im HBM-Stack

HBM8 als leistungsstärkster Ausbau

Die Roadmap endet mit HBM8, das in 2038 erwartet wird. Diese Generation wird die Pin-Geschwindigkeiten über eine 16.384-Bit-Schnittstelle auf 32 Gbps steigern und damit erstaunliche 64 TB/s pro Stack bieten. Die Speicherkapazitäten pro Stack werden zwischen 200 und 240 GB liegen, wobei die Leistungsaufnahme auf 180 W steigen wird. Zur Wärmeableitung werden integrierte Kühltechnologien auf Paketebene integriert.

Die Hauptmerkmale des HBM8-Speicherstandards umfassen:

- Datenrate: 32 Gbps

- Anzahl der I/Os: 16384

- Gesamtbandbreite: 64 TB/s

- Anzahl der Die-Stacks: 20/24-Hi

- Kapazität pro Die: 80 Gb

- Kapazität pro HBM: 200/240 GB

- Gehäuse-Leistung pro HBM: 180 W

- Verpackungsmethode: Bump-Less Cu-Cu-Direktverbindung

- Kühlmethode: Integrierte Kühlung

- Koaxialer TSV / Full-3D GPU-HBM

- HBM-zentriertes Computing

- Vollständiges Speichernetzwerk

- Doppelseitiger Interposer

hybride HBM-HBF-Architekturen

Über DRAM hinaus deutete die Präsentation auch hybride HBM-HBF-Architekturen (High-Bandwidth Flash) an, die für KI-Inferenz-Workloads ausgelegt sind. Diese Systeme werden DRAM und NAND-Flash über hochgeschwindigkeitsfähige Durchkontaktierungen kombinieren, sodass Beschleuniger in Multi-Chiplet-Umgebungen Bandbreiten im Petabyte-Bereich erreichen können. Diese Entwicklungen unterstreichen den Bedarf an immer komplexeren Speicherarchitekturen, um die Rechenanforderungen der nächsten Generation in KI- und Rechenzentrumsplattformen zu erfüllen.