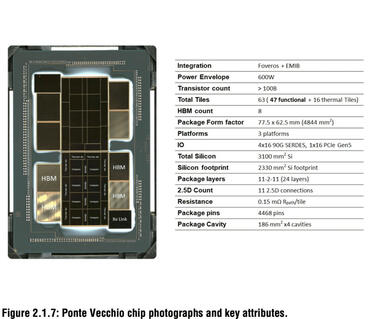

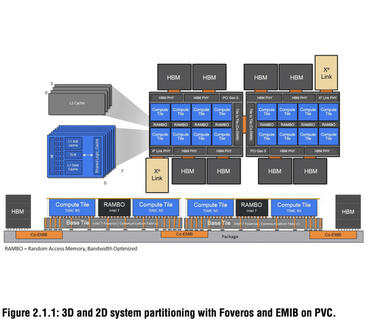

Es gibt insgesamt 63 Tiles, von denen 16 für die Berechnung reserviert sind, acht werden für den RAMBO-Cache verwendet, zwei sind Foveros-Basis-Tiles, zwei stellen Xe-Link-Tiles dar, acht sind HBM2E-Tiles und die EMIB-Verbindung nimmt 11 Tiles ein. Dies ergibt insgesamt etwa 47 Tiles. Zusätzliche 16 Tiles dienen der thermischen Übertragung, die in Ponte Vecchio verwendet werden, um die massive TDP-Leistung dieses Beschleunigers zu gewährleisten.

Intel hat auch spannende Details über den RAMBO-Cache verraten. Diese neuartige SRAM-Technologie verwendet vier Bänke mit 3,75 MB Gruppen von insgesamt 15 MB pro Kachel. Sie sind mit einer Geschwindigkeit von 1,3 TB/s pro Chip mit der Fabric verbunden. Im Gegensatz dazu sind die Rechenkacheln mit einer Geschwindigkeit von 2,6 TB/s mit der Chipstruktur verbunden. Mit acht RAMBO-Cache-Kacheln bekommen wir also zusätzlichen 120 MB SRAM. Das Basis-Tile ist ein 646 mm² großer Chip, der im Intel 7-Halbleiterverfahren hergestellt wird und 17 Schichten enthält. Darin enthalten ist ein Speichercontroller, die voll integrierten Spannungsregler (FIVR), die Energieverwaltung, der 16-Lane-PCIe-5.0-Anschluss und die CXL-Schnittstelle.

Die Gesamtfläche von Ponte Vecchio ist ziemlich beeindruckend, da 47 aktive Tiles 2.330 mm² einnehmen, während die Gesamtfläche auf 3.100 mm² ansteigt, wenn wir die thermischen Dies einbeziehen. Und natürlich ist das gesamte Gehäuse mit 4.844 mm² viel größer und mit 4.468 Pins an das System angeschlossen.

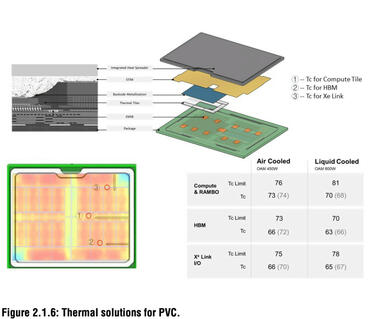

Intel wählte den N5-Knoten von TSMC für die Compute-Tiles, während die Xe-Link-Tiles den N7-Knoten von TSMC verwenden. Für den RAMBO-Cache und die Foveros-Basiskacheln wird der Intel 7-Prozess verwendet. Der gesamte Chip ist auf maximale Effizienz und Leistung ausgelegt und hat eine TDP von 450 Watt bei Luftkühlung, während die Wasserkühlung eine Erhöhung der TDP auf 600 Watt ermöglicht. Ponte Vecchio ist für den Betrieb bei 63-81°C ausgelegt - eine Standardanforderung für diese Art von Produkten, die im HPC-Bereich eingesetzt werden.