X570 „Valhalla“ mit 28 PCIe gen 4 Lanes

Beim dem X570 Chipsatz soll AMD bei der Entwicklung selbst Hand angelegt haben und nicht wie beim X470 und X370 auf die Originaldesigns von ASMedia setzen. Wie bereits aus der Gerüchteküche mehrfach berichtet, soll die neue Plattform u.a. auf die vierte Generation des PCIe-Standards setzen. Von diesen stehen insgesamt 28 Lanes bereit.

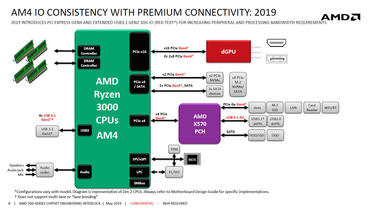

Im Vergleich zu PCIe Gen 3 ist die Bandbreite auf 16 GT/s verdoppelt worden. 16 Lanes werden dabei für die Anbindung der dedizierten Grafikkarte verwendet, wobei die Konfiguration auf 2 x 8 Lanes wechselt, falls zwei Karten verwendet werden.

Zwei PCIe Gen 4 Lanes werden für Anbindung an NVMe SSDs genutzt, wodurch die gleiche Bandbreite wie von 4 x PCIe Gen 3 Lanes erreicht wird. Zwei weitere PCIe Gen 4 Lanes werden für SATA-Laufwerke verwendet, was überdimensioniert erscheint.

Der X570 Chipsatz wird mittels vier PCIe Gen 4 Lanes mit dem Sockel verbunden. Der theoretische Datendurchsatz sollte damit 64 GB/s betragen, was eine Verdopplung zum Vorgänger bedeuten würde. Der Chipsatz nutzt dann weitere PCIe Gen 4 Lanes für die Anbindung von zusätzlichen PCIe-Slots, M.2-SSDs und Netzwerkkarten. Dieser kümmert sich auch um die USB 3.1 Gen 2 und USB 2.0 Ports und SATA Ports.

Vier weitere Lanes werden dem Blockidagram zu Folge für USB 3.1 Gen 2 genutzt, die direkt an den Ryzen 3000 AM4 Sockel andocken. Dabei sollte es um OCuLink-2 bzw. Thunderbolt Schnittstellen handeln, die eGPUs und andere Peripherie direkt anbinden.

15 Watt TDP

Die Informationsquelle hat außerdem eine Angabe zur TDP des neuen Chipsatzes gemacht, die nun 15 Watt betragen soll. Sollte sich dies bewahrheiten, würde dies die Verdreifachung der TDP bedeuten und die Verwendung von aktiven Kühlern erklären.