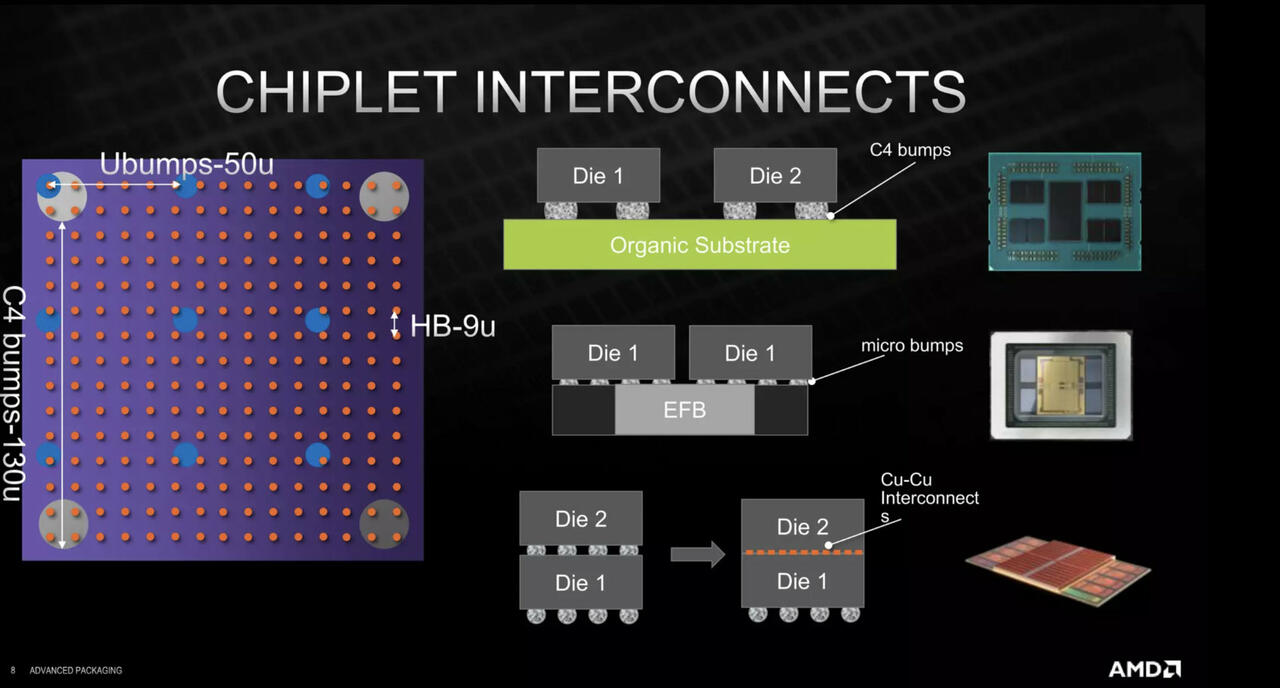

AMD 3D-V-Cache-Aufbau (Bild © AMD)

AMD 3D-V-Cache-Aufbau (Bild © AMD)

Die Leaks sprechen davon, dass Intel CPU-Varianten listet, die zwei gestapelte Cache-Blöcke anstelle von einem einem beinhalten, wodurch der gesamte L3-Cache von bisher erwarteten 140 MB auf über 200 MB ansteigt. Dieser Schritt deckt sich mit den Leaks über AMDs Zen 5-basierte Chips der nächsten Generation, die Berichten zufolge ein Dual X3D-Chiplet-Design enthalten werden. AMD hat Zen 5 X3D bereits in einer Single-Chiplet-Variante ausgeliefert, was auf einen kürzeren Weg zur Marktreife hindeutet.

Das erneute Interesse an massiven L3-Caches ist auf die steigenden Anforderungen von KI-Anwendungen, großen Sprachmodellen und speicherintensiven Workloads zurückzuführen, die von einer erhöhten Cache-Kapazität erheblich profitieren. Obwohl weder die dualen BLLC-CPUs von Intel noch die dualen X3D-Chips von AMD offiziell bestätigt wurden, scheint sich die Branche auf cache-lastige CPU-Architekturen als Schlüssel für die zukünftige Rechenleistung vorzubereiten.

Eine große technische Hürde besteht jedoch darin, heterogene Cache-Topologien ohne Leistungseinbußen zu verwalten. Asymmetrische Zugriffslatenzen und Probleme bei der Zeitplanung könnten sich auf die Arbeitslasten auswirken, wenn sie in der Firmware und den Betriebssystemschichten nicht richtig behandelt werden. Da beide Unternehmen jedoch Designs mit hoher Bandbreite und hohem Cache anstreben, könnte es bei den CPUs der nächsten Generation schon weit vor 2027 zu einer grundlegenden Änderung der Architektur kommen.

Intels Nova Lake-Plattform, die angeblich die Basis für die neuen Cache-lastigen Modelle bildet, wird nicht vor Ende 2026 erwartet, während AMDs Dual-X3D-CPUs je nach Marktreife früher auf den Markt kommen könnten.