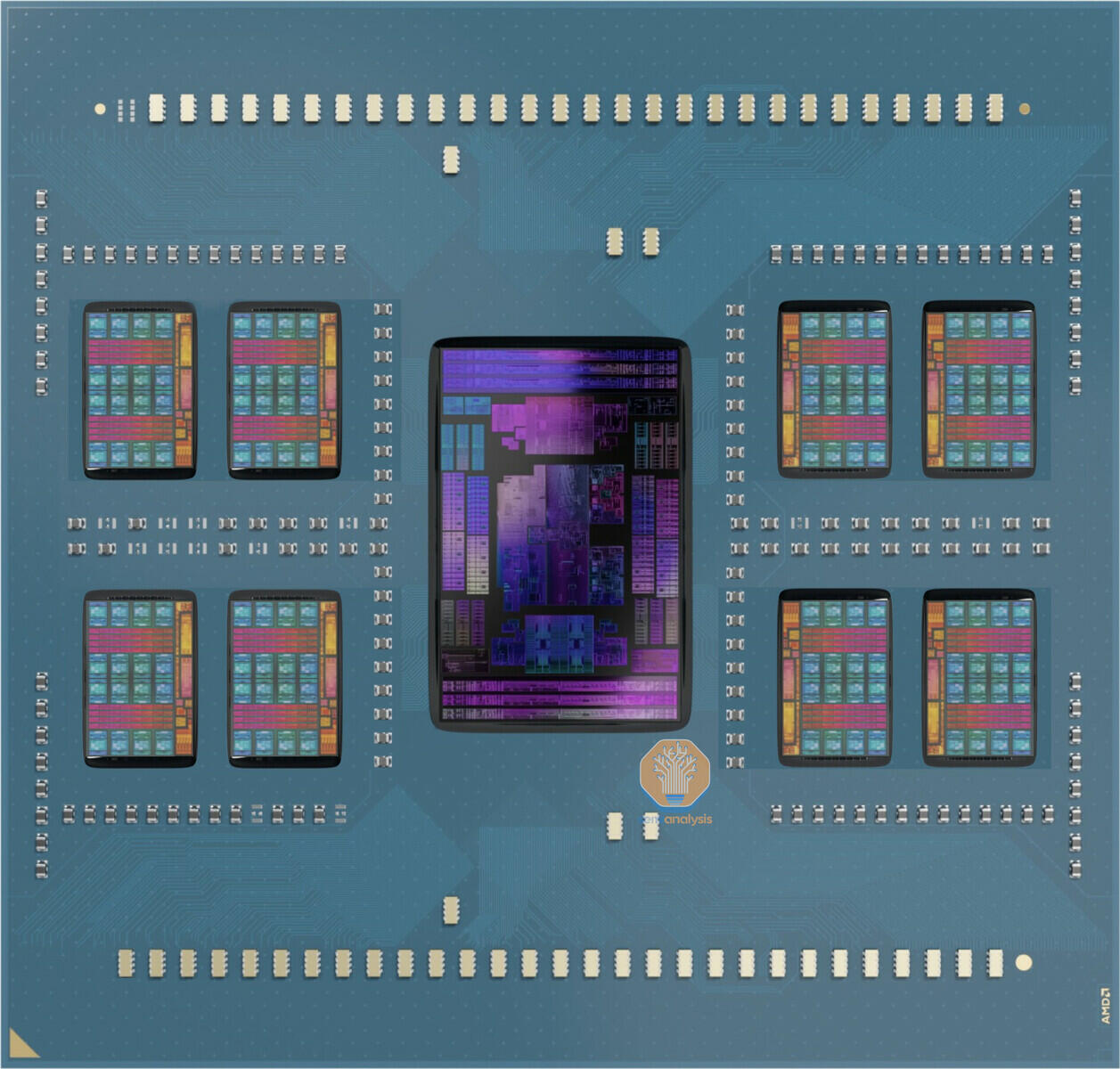

EPYC 9754-Prozessor mit 128 Kernen

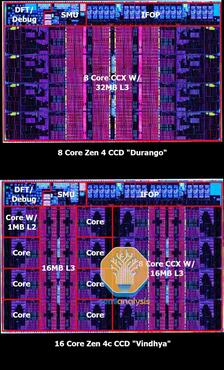

Die geringere Größe des Zen-4c im Vergleich zu einem regulären "Zen 4"-Kern ermöglicht es AMD die CPU-Core-Dies (kurz CCD) mit 16 Kernen herzustellen. Die "Zen 4" Architektur konnte nur 8-Kern-CCDs hervorbringen. Der "Zen 4c"-CCD mit 16 Kernen, der im gleichen 5-nm-EUV-Prozess wie der "Zen 4"-CCD mit 8 Kernen hergestellt wird, beinhaltet intern zwei CPU-Kernkomplexe (CCX), die je acht "Zen 4c"-Kerne enthalten. Jeder CCX teilt sich einen 16 MB L3-Cache mit seinen Kernen. Der SemiAnalysis-Bericht gibt auch preis, dass der "Zen 4c"-Kern die dedizierte L2-Cache-Größe von 1 MB beibehält. Eine wichtige Enthüllung ist die erste Schätzung der Die-Größe. Diese besagt, dass der 16-Kern "Zen 4c" CCD nur ca. 9,6% mehr Die-Fläche hat als der 8-Kern "Zen 4" CCD. Das ist eine beachtliche Leistung.

Dionysus Zen 4c-Kerne

Server-I/O-Die bleibt gleich

Der Server-I/O-Die (sIOD) wird in einem 6-nm-Prozess gefertigt und ist identisch mit dem Server-I/O-Die in den EPYC "Genoa"-Prozessoren. Er enthält eine 12-Kanal (24 Sub-Kanäle) DDR5-Speicherschnittstelle und einen PCI Express 5.0 x128 Root-Komplex.