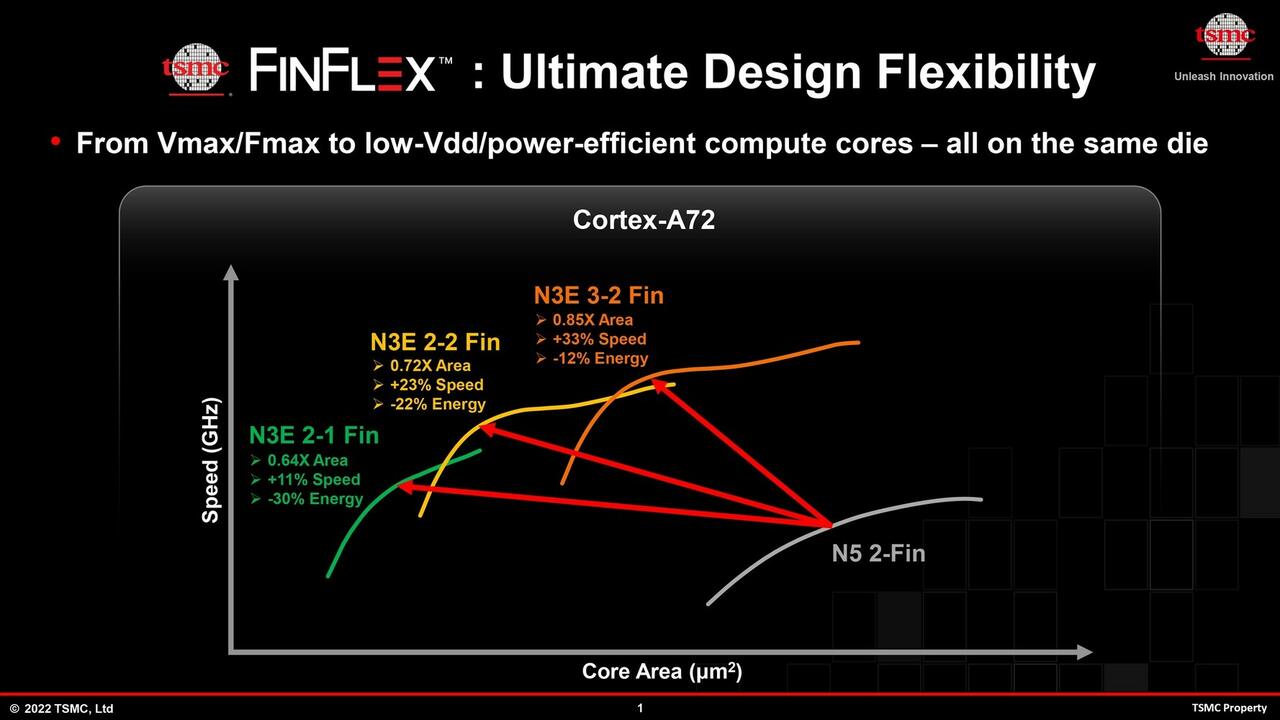

TSMC FinFlex (Bild © TSMC)

TSMC FinFlex (Bild © TSMC)

TSMC FINFLEX für N3 und N3E

Die branchenführende N3-Technologie von TSMC, die im Laufe des Jahres 2022 in die Serienproduktion gehen soll, wird mit der revolutionären TSMC FINFLEX-Architekturinnovation ausgestattet sein, die Designern eine unvergleichliche Flexibilität bietet. Die TSMC FINFLEX-Innovation bietet eine Auswahl verschiedener Standardzellen mit einer 3-2-Finnenkonfiguration für höchste Leistung, einer 2-1-Finnenkonfiguration für beste Leistungseffizienz und Transistordichte und einer 2-2-Finnenkonfiguration, die ein Gleichgewicht zwischen beiden für effiziente Leistung bietet. Mit der FINFLEX-Architektur von TSMC können Kunden System-on-Chip-Designs erstellen, die genau auf ihre Bedürfnisse abgestimmt sind, mit Funktionsblöcken, die die beste optimierte Rippenkonfiguration für die gewünschten Leistungs-, Energie- und Flächenziele implementieren und auf demselben Chip integriert sind.

N2-Technologie

TSMCs N2-Technologie stellt einen weiteren bemerkenswerten Fortschritt gegenüber N3 dar, mit einer 10-15%igen Geschwindigkeitsverbesserung bei gleicher Leistung bzw. einer 25-30%igen Leistungsreduzierung bei gleicher Geschwindigkeit, wodurch eine neue Ära effizienter Leistung eingeläutet wird. N2 wird eine Nanosheet-Transistor-Architektur aufweisen, die eine Verbesserung der Leistung und Energieeffizienz über einen ganzen Knoten hinweg ermöglicht, um Produktinnovationen der nächsten Generation von TSMC-Kunden zu ermöglichen. Die N2-Technologieplattform umfasst neben der Mobile-Compute-Basisversion auch eine Hochleistungsvariante sowie umfassende Chiplet-Integrationslösungen. Der Produktionsstart für die N2 Nodes ist für 2025 eingeplant.

Erweiterung der Ultra-Low-Power-Plattform

Aufbauend auf dem Erfolg der N12e-Technologie, die auf dem Technologie-Symposium 2020 angekündigt wurde, entwickelt TSMC N6e, die nächste Evolutionsstufe der Prozesstechnologie, die darauf abgestimmt ist, die für Edge-KI- und IoT-Geräte erforderliche Rechenleistung und Energieeffizienz zu bieten. N6e wird auf dem fortschrittlichen 7-nm-Prozess von TSMC basieren und soll eine dreimal höhere Logikdichte als N12e aufweisen. Er wird Teil der Ultra-Low-Power-Plattform von TSMC sein, einem umfassenden Portfolio von Logik-, HF-, Analog-, eingebetteten nichtflüchtigen Speicher- und Power-Management-IC-Lösungen, die auf Anwendungen in der Edge-KI und im Internet der Dinge ausgerichtet sind.

TSMC 3DFabric 3D Silicon Stacking Solutions

Außerdem sind zwei bahnbrechende Kundenanwendungen der TSMC-SoIC-Chipstacking-Lösung gezeigt worden:

- Die weltweit erste SoIC-basierte CPU, die die Chip-on-Wafer (CoW)-Technologie nutzt, um SRAM als Level-3-Cache zu stapeln

- Eine bahnbrechende intelligente Verarbeitungseinheit, die mit Hilfe der Wafer-on-Wafer (WoW)-Technologie auf einem Deep-Trench-Kondensator-Die gestapelt wird.

- N7-Chips werden bereits für CoW und WoW produziert, die Unterstützung der N5-Technologie ist für 2023 geplant. Um die Kundennachfrage nach SoIC und anderen 3DFabric-Systemintegrationsdiensten von TSMC zu befriedigen, soll die weltweit erste vollautomatische 3DFabric-Fabrik in der zweiten Jahreshälfte 2022 die Produktion aufnehmen.